Time: 2025-03-14 11:16:17View:

Creating a sonar fish finder or ultrasonic underwater imaging system using an FPGA (Field-Programmable Gate Array) is a complex but rewarding project. FPGAs are ideal for this application due to their high-speed processing capabilities, parallel processing architecture, and ability to handle real-time signal processing. Below is a step-by-step guide to help you design such a system:

Sonar Principle: Sonar systems emit sound waves (ultrasonic pulses) into the water and measure the time it takes for the echoes to return. The time delay and amplitude of the echoes are used to determine the distance and shape of objects underwater.

Key Components:

Transducer: Converts electrical signals into sound waves and vice versa.

Signal Processing: Analyzes the received echoes to extract useful information.

Display: Visualizes the processed data (e.g., depth, fish location, or underwater terrain).

The system can be divided into the following modules:

Transducer Interface: Generates ultrasonic pulses and receives echoes.

Signal Processing: Processes the received signals to extract useful data.

Data Visualization: Displays the processed data on a screen.

Control Logic: Manages the overall system operation.

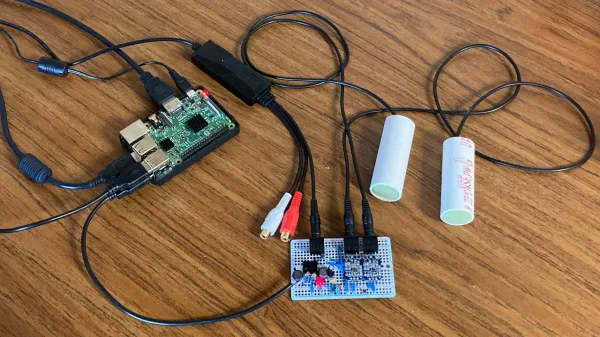

FPGA Development Board (e.g., Xilinx Zynq, Intel Cyclone, or Lattice ECP5).

Ultrasonic Transducer (appropriate frequency for underwater imaging, e.g., 50 kHz–200 kHz).

Analog Front-End (AFE) Circuitry:

Pulse Generator: To drive the transducer.

Amplifier: To amplify weak echo signals.

Filter: To remove noise from the received signals.

ADC: To digitize the analog echo signals.

Display (e.g., LCD or VGA monitor).

Power Supply.

Additional Components: Resistors, capacitors, op-amps, etc.

Pulse Generation:

Use the FPGA to generate a high-frequency pulse (e.g., 50 kHz–200 kHz) to drive the transducer.

Implement a pulse generator module in the FPGA using a counter and a clock divider.

Echo Reception:

Use the ADC to digitize the received echo signals.

Implement an interface to read the ADC data into the FPGA.

Filtering:

Implement digital filters (e.g., FIR or IIR) in the FPGA to remove noise from the received signals.

Time-of-Flight Calculation:

Measure the time delay between the transmitted pulse and the received echo to calculate the distance to the object.

Use a counter in the FPGA to measure the time delay.

Beamforming (Optional):

If using multiple transducers, implement beamforming algorithms to improve spatial resolution.

Data Extraction:

Extract features such as echo amplitude, frequency, and phase to identify objects (e.g., fish or underwater terrain).

Display Interface:

Use an HDMI, VGA, or LCD interface to display the processed data.

Implement a graphics module in the FPGA to render the sonar image.

Data Formatting:

Convert the processed data into a format suitable for display (e.g., depth vs. amplitude plot).

Implement a state machine in the FPGA to manage the overall system operation:

Transmit pulses.

Capture and process echoes.

Update the display.

Hardware Description Language (HDL):

Use Verilog or VHDL to design the FPGA logic.

IP Cores:

Use pre-built IP cores for complex functions like FFT (Fast Fourier Transform) or FIR filters.

Simulation and Testing:

Simulate the design using tools like Xilinx Vivado or Intel Quartus.

Test the system with a transducer in a water tank before deploying it in open water.

1. Transmit Pulse:

The FPGA generates a pulse and sends it to the transducer.

2. Receive Echo:

The transducer receives the echo, and the AFE circuitry amplifies and filters the signal.

The ADC digitizes the signal and sends it to the FPGA.

3. Process Data:

The FPGA processes the echo data to calculate distance and extract features.

4. Display Results:

The FPGA sends the processed data to the display for visualization.

Multiple Transducers:

Use an array of transducers for better spatial resolution and beamforming.

3D Imaging:

Implement advanced signal processing algorithms to create 3D underwater images.

Wireless Communication:

Add a wireless module (e.g., Wi-Fi or Bluetooth) to transmit data to a remote device.

Noise Reduction:

Underwater environments can be noisy. Use advanced filtering techniques to improve signal quality.

Real-Time Processing:

Ensure the FPGA design can process data in real time to provide accurate and timely results.

Power Efficiency:

Optimize the design for low power consumption, especially for battery-operated systems.

FPGA Development Tools:

Xilinx Vivado, Intel Quartus, or Lattice Diamond.

Simulation Tools:

MATLAB or Python for algorithm development and simulation.

Reference Designs:

Look for open-source sonar or ultrasonic imaging projects for inspiration.

By following these steps, you can design and implement a sonar fish finder or ultrasonic underwater imaging system using an FPGA. Let me know if you need further assistance with specific parts of the design!