Time: 2025-05-20 11:37:57View:

To use the Xilinx Artix-7 FPGA (e.g., XC7A100T) with Vivado for synthesis, you need to follow a structured process involving project setup, HDL coding, synthesis, implementation, and bitstream generation. Here's a step-by-step guide for beginners or intermediate users:

Vivado Design Suite (Download from AMD/Xilinx website)

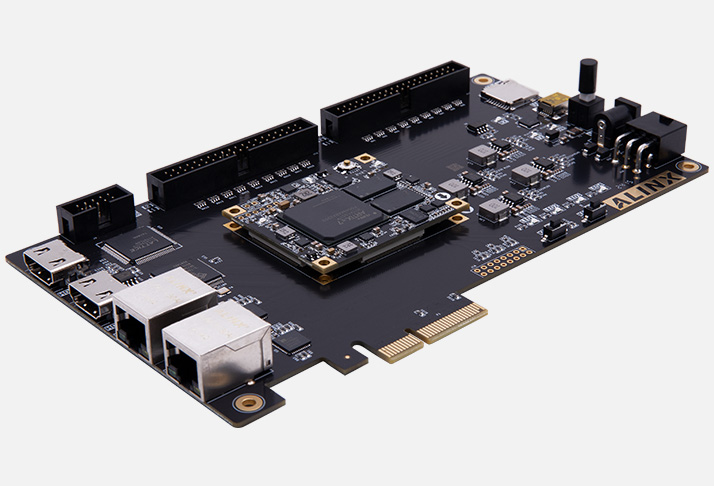

A supported Artix-7 board (e.g., Digilent Nexys A7 with XC7A100T chip)

Basic knowledge of Verilog or VHDL

Open Vivado.

Click Create New Project.

Enter a project name and directory.

Choose RTL Project (don’t check "Do not specify sources").

Add your HDL files (Verilog or VHDL).

Select the FPGA part:

Family: Artix-7

Package: CSG324 (common for many boards)

Speed grade: -1

Part: xc7a100tcsg324-1

For Artix-7 XC7A100T:

Example (Verilog) – A simple LED blinker:

verilog module led_blinker( input clk, // Clock input output reg led // LED output ); reg [23:0] counter; always @(posedge clk) begin counter <= counter + 1; if (counter == 24'd10000000) led <= ~led; end endmodule

You need an XDC (Xilinx Design Constraints) file to map logical signals to FPGA pins.

Example:

xdc ## Clock input set_property PACKAGE_PIN E3 [get_ports clk] set_property IOSTANDARD LVCMOS33 [get_ports clk] ## LED output set_property PACKAGE_PIN H17 [get_ports led] set_property IOSTANDARD LVCMOS33 [get_ports led]

Pin names depend on your board. Refer to the board’s User Manual or Master XDC File.

Click Run Synthesis in the Flow Navigator.

Vivado will:

Parse your code

Optimize logic

Generate RTL netlist

If it completes successfully, continue.

Click Run Implementation.

Vivado places and routes your design into the FPGA's fabric.

Review the timing summary to ensure constraints are met.

Click Generate Bitstream.

After generation, Vivado produces a .bit file (used to configure the FPGA).

If you have a development board connected:

Open Hardware Manager.

Connect to the board via USB/JTAG.

Program the FPGA with the .bit file.

Always verify your pin locations with the board’s reference manual.

Use simulation (with Vivado’s built-in simulator or ModelSim) before synthesis.

Use IP Integrator for complex systems like MicroBlaze or AXI-based designs.