Time: 2025-02-25 13:42:15View:

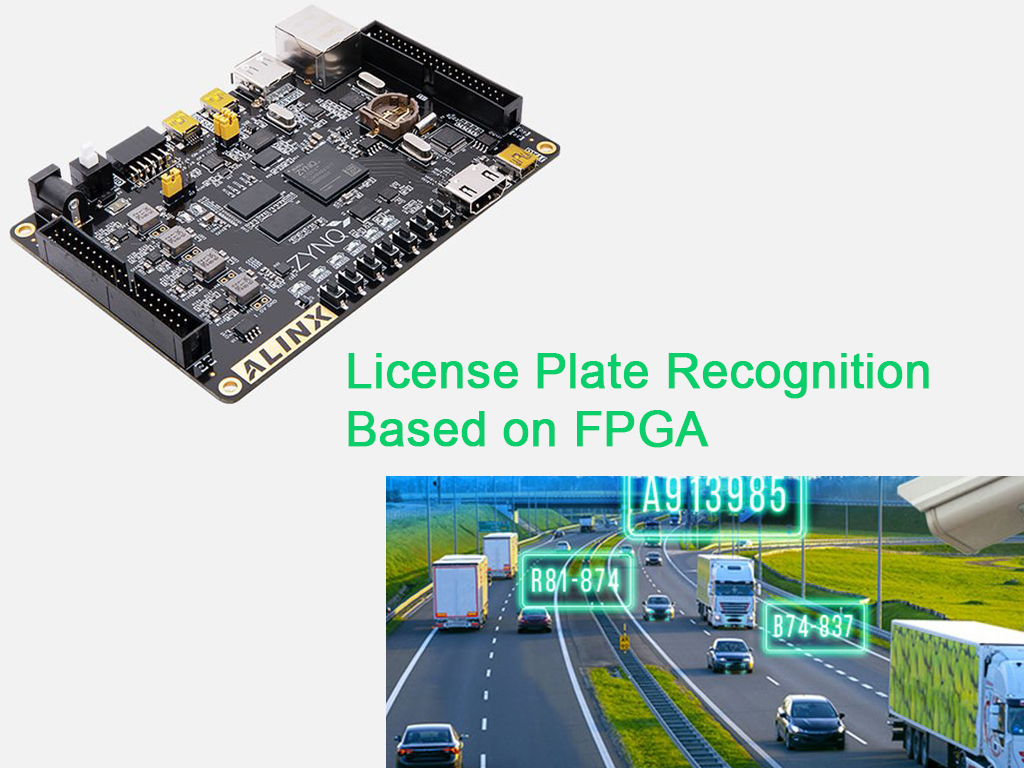

License Plate Recognition (LPR) systems are widely used in traffic management, parking systems, and security applications. Implementing such a system on an FPGA (Field-Programmable Gate Array) offers advantages like high-speed processing, parallel computation, and real-time performance. Below is an overview of how License Plate Recognition can be implemented using an FPGA:

Image Acquisition:

A camera captures the image of the vehicle's license plate.

The image is preprocessed (e.g., resizing, noise reduction) before being fed into the FPGA.

License Plate Detection:

The FPGA processes the image to locate the license plate region.

Techniques like edge detection, morphological operations, or machine learning algorithms (e.g., Haar cascades) can be implemented in hardware.

Character Segmentation:

The detected license plate region is further processed to isolate individual characters.

This involves binarization (converting to black and white), contour detection, and bounding box extraction.

Optical Character Recognition (OCR):

The segmented characters are recognized using OCR algorithms.

Pre-trained models (e.g., neural networks) or template matching can be implemented on the FPGA.

Output:

The recognized characters are converted into text and sent to a display, database, or control system.

High-Speed Processing:

FPGAs can process images in real-time due to their parallel processing capabilities.

Ideal for applications requiring low latency, such as toll booths or traffic monitoring.

Customizability:

The FPGA can be reprogrammed to adapt to different license plate formats, lighting conditions, or camera resolutions.

Power Efficiency:

FPGAs are more power-efficient than general-purpose processors for specific tasks like image processing.

Parallelism:

Tasks like edge detection, filtering, and character recognition can be executed simultaneously, improving performance.

Real-Time Operation:

FPGAs are well-suited for real-time applications, ensuring quick response times.

Complexity of Implementation:

Designing and optimizing hardware for image processing and OCR can be challenging.

Requires expertise in FPGA programming (e.g., VHDL or Verilog).

Resource Constraints:

FPGAs have limited logic cells, memory, and DSP blocks, which may restrict the complexity of the algorithms.

Algorithm Optimization:

Algorithms must be optimized for hardware implementation, which may involve trade-offs between accuracy and resource usage.

Cost:

High-performance FPGAs can be expensive, especially for large-scale deployments.

Hardware Design:

Use an FPGA development board (e.g., Xilinx Zynq, Intel Cyclone) with sufficient resources for image processing.

Implement image acquisition using a camera interface (e.g., HDMI, MIPI).

Image Preprocessing:

Design hardware modules for tasks like grayscale conversion, noise reduction, and edge detection.

License Plate Detection:

Implement algorithms like Sobel edge detection or morphological operations to identify the license plate region.

Character Segmentation:

Develop modules for binarization, contour detection, and character isolation.

OCR Implementation:

Use hardware-accelerated neural networks or template matching for character recognition.

Pre-trained models can be deployed on the FPGA using tools like Xilinx Vitis AI or Intel OpenVINO.

System Integration:

Combine all modules into a cohesive system and test with real-world data.

Optimize for performance, accuracy, and resource utilization.

FPGA Platforms: Xilinx Zynq, Intel Cyclone, or Lattice ECP5.

Development Tools: Xilinx Vivado, Intel Quartus, or Lattice Diamond.

Image Processing Libraries: OpenCV (for algorithm prototyping) or custom HDL implementations.

Machine Learning Frameworks: TensorFlow Lite, PyTorch (for OCR model training).

Traffic Monitoring:

Automated toll collection and traffic law enforcement.

Parking Systems:

License plate recognition for entry/exit management.

Security:

Vehicle tracking and access control.

Smart Cities:

Integration with IoT systems for urban traffic management.

Implementing License Plate Recognition on an FPGA offers a powerful solution for real-time, high-performance applications. While the development process can be complex, the benefits of speed, flexibility, and efficiency make FPGAs an attractive choice for LPR systems. By leveraging hardware acceleration and parallel processing, FPGA-based LPR systems can achieve high accuracy and low latency, making them suitable for a wide range of applications.