Time: 2025-05-07 11:14:13View:

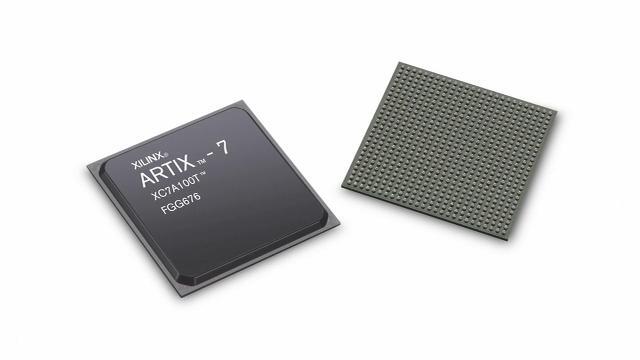

The Xilinx 7 Series FPGAs (including Artix-7, Kintex-7, and Virtex-7) offer several key logic advantages that make them highly efficient for a wide range of applications, from embedded systems to high-performance computing. Below are the main architectural and performance benefits:

High-performance logic fabric based on 28nm HKMG (High-K Metal Gate) technology, balancing power efficiency and speed.

Configurable Logic Blocks (CLBs) with 6-input LUTs (Look-Up Tables) that can be split into two 5-input LUTs, improving logic density and flexibility.

Dedicated carry chains for fast arithmetic operations (e.g., adders, counters).

Wide distributed RAM (LUT-RAM) and shift registers, reducing the need for block RAM in small memory applications.

Mixed-Mode Clock Managers (MMCM) and Phase-Locked Loops (PLLs) for precise clock synthesis, deskewing, and jitter reduction.

Low-power clocking with dynamic clock gating, critical for battery-operated devices.

Gigabit Transceivers (GTX/GTH/GTZ):

Up to 28.05 Gbps (GTZ in Virtex-7) for high-speed serial protocols (PCIe Gen3, SATA, 10G Ethernet).

Low-power modes for energy-sensitive applications.

Integrated PCIe® Gen2/Gen3 blocks, reducing external PHY requirements.

DSP48E1 slices (in Artix-7/Kintex-7/Virtex-7) support:

Multiply-Accumulate (MAC) operations at up to 550 MHz.

Flexible 25x18 multipliers with optional pipelining.

Bitwise logic operations, enabling custom accelerators (e.g., AI/ML inference).

Block RAM (36 Kb BRAM) with true dual-port access, configurable as FIFOs or caches.

UltraRAM (in Virtex-7) – 288 Kb memory blocks for large buffer storage (e.g., video frame buffers).

ECC support for error correction in mission-critical systems.

28nm process reduces static/dynamic power vs. older FPGAs.

Power gating for unused logic regions.

Hysteresis-based I/O standards (HSTL, SSTL) for low-power memory interfaces.

Same architecture across Artix-7, Kintex-7, Virtex-7, enabling easy migration.

AES/SHA-256 bitstream encryption to prevent IP theft.

SEU (Single-Event Upset) mitigation in Virtex-7 for radiation-tolerant designs.

| Feature | Xilinx 7 Series | Intel Cyclone/Arria 10 |

|---|---|---|

| LUT Structure | 6-input LUT (flexible) | 6-input ALM (less granular) |

| DSP Slices | DSP48E1 (higher MHz) | Variable precision DSP |

| Transceivers | Up to 28.05 Gbps | Up to 17.4 Gbps (Arria 10) |

| Memory | UltraRAM (Virtex-7) | No equivalent |

✔ High-speed networking (100G Ethernet, packet processing)

✔ Embedded vision (real-time 4K video pipelines)

✔ Aerospace/defense (radar, secure comms)

✔ AI acceleration (DSP-based CNN inference)

The Xilinx 7 Series excels in logic density, power efficiency, and high-speed I/O, making it a versatile choice for both cost-sensitive and high-performance designs. Its unified architecture ensures scalability, while advanced DSP and memory resources enable complex compute tasks.

For low-power designs, Artix-7 is ideal, while Virtex-7 dominates in ultra-high-performance applications.