Time: 2025-05-23 11:31:29View:

Here's a clear explanation of how PAL, PLA, and FPGA work, focusing on their internal logic and how they implement digital functions:

A PLA consists of:

A programmable AND array

A programmable OR array

Implements sum-of-products (SOP) logic:F = (A AND B) OR (A' AND C) etc.

You program which input combinations go to the AND gates.

Then, you program which product terms (AND outputs) go to the OR gates.

ngin Inputs → Inverters → Programmable AND → Programmable OR → Outputs

Fully programmable logic.

Flexible and general-purpose.

Good for implementing multiple logic functions sharing terms.

A PAL is a simplified version of a PLA:

A programmable AND array

A fixed OR array

You still implement SOP logic, but with less flexibility:

You can only OR together a fixed number of product terms.

So, complex functions may not fit directly.

scss Inputs → Inverters → Programmable AND → Fixed OR → Outputs

Faster than PLA due to simpler structure.

Less flexible, but more reliable and cheaper.

Often used for simple control logic or glue logic.

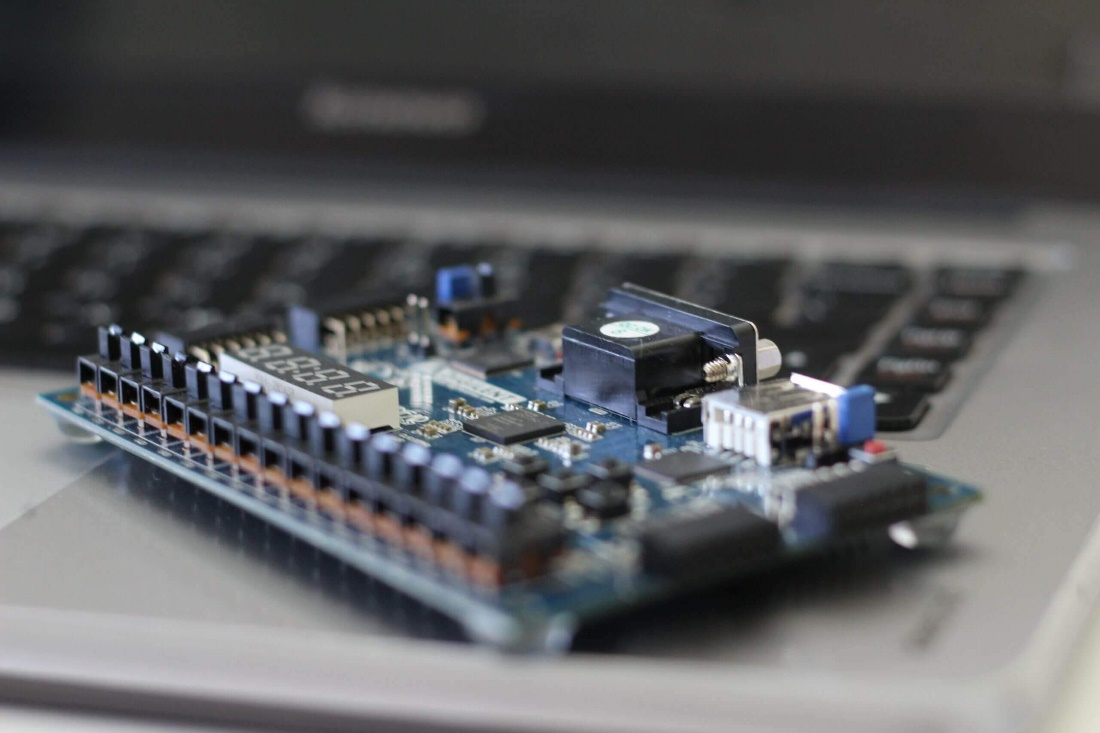

An FPGA is a large grid of:

Configurable Logic Blocks (CLBs) with Look-Up Tables (LUTs)

Programmable interconnects

I/O blocks

Each LUT stores the truth table of a logic function (like a tiny ROM).

You program which logic goes into each LUT.

Then you configure how the logic blocks are wired together using programmable switches.

objectivec Inputs → Routing → CLBs (LUT + FF) → Routing → Outputs

Very flexible: can implement complex digital systems (even CPUs).

Supports sequential logic (flip-flops), RAM, DSP, etc.

Programmable via HDL (VHDL/Verilog) and tools like Vivado or Quartus.

| Feature | PLA | PAL | FPGA |

|---|---|---|---|

| AND Array | Programmable | Programmable | Implemented via LUTs |

| OR Array | Programmable | Fixed | Implemented via LUTs & routing |

| Flexibility | High | Medium | Very High |

| Complexity Limit | Medium | Low to Medium | Very High |

| Speed | Moderate | Fast | High (with pipelining) |

| Use Case | Basic digital logic | Simple control logic | Complex systems (e.g. AI, SoC) |