Time: 2025-05-26 10:59:55View:

Implementing HDMI transmission on an FPGA involves handling TMDS (Transition Minimized Differential Signaling) encoding, EDID (Extended Display Identification Data), HDCP (High-bandwidth Digital Content Protection), and sometimes audio embedding. Below is a structured approach to implementing HDMI transmission using an FPGA, covering both Xilinx and Lattice solutions.

HDMI uses TMDS (3 differential pairs for RGB + 1 for clock).

Requires serialization (typically at 5x pixel clock, e.g., 165 MHz for 1080p60).

Must follow HDMI/DVI spec (8b/10b encoding, preambles, control periods).

The sink (monitor) provides EDID over DDC (I²C).

The FPGA must:

Respond to I²C reads from the source (PC/player).

Store EDID in EEPROM or internal memory.

Requires authentication and encryption (complex, often licensed IP).

Mostly needed for commercial products.

Pack audio samples into HDMI data islands.

Requires I2S input and proper HDMI packetization.

Spartan-6 (Low-cost, older but proven for HDMI).

Artix-7 (Better for 4K, more logic resources).

Zynq-7000 (If you need ARM + FPGA for advanced processing).

TMDS Serializer

Use OSERDES (Xilinx primitives) for high-speed serialization.

Example: For 1080p60 (148.5 MHz pixel clock), serialize at 5x (742.5 Mbps per lane).

EDID Handling

Use Soft I²C Core (Xilinx provides AXI IIC IP).

Store EDID in Block RAM or external EEPROM.

HDCP (If Needed)

Licensed IP from Synopsys or Xilinx (expensive).

Example Projects:

Digilent’s HDMI PMOD (Spartan-6 based).

FPGA4Fun HDMI examples (Basic DVI, no audio).

Supports higher resolutions (4K with Artix-7).

More resources for video processing (scaling, switching).

Higher power & cost.

Complex development (Vivado).

TMDS Serializer

Use Lattice’s SERDES blocks (like ODDR + LVDS).

Example: MachXO3 supports HDMI 1.4 (up to 1080p60).

EDID Handling

Use I²C soft core (Lattice provides reference designs).

Store EDID in internal Flash or EEPROM.

HDCP (If Needed)

Lattice offers HDCP 1.4 IP (for ECP5).

Example Projects:

Lattice HDMI SiI9396 Demo (MachXO3).

OpenFPGA HDMI projects (ECP5-based).

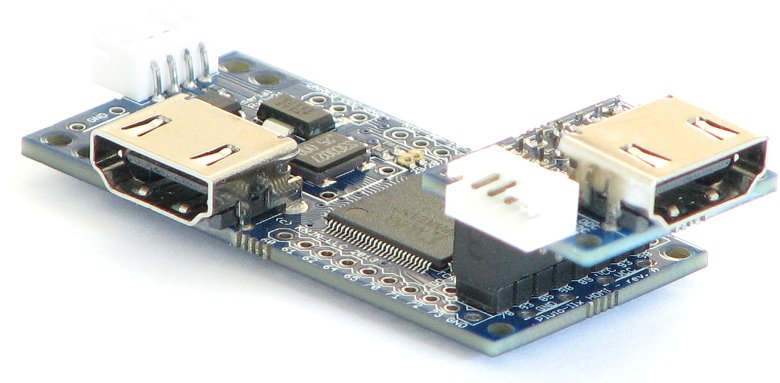

Lower power & cost (great for dongles, adapters).

Easier tools (Lattice Radiant/Diamond).

Limited to 1080p on MachXO3, needs ECP5 for 4K.

Fewer high-speed interfaces than Xilinx.

| Feature | Xilinx (Artix-7/Spartan-6) | Lattice (MachXO3/ECP5) |

|---|---|---|

| Max Resolution | 4K @ 60Hz (Artix-7) | 1080p (MachXO3), 4K (ECP5) |

| Power Consumption | Higher (~1-2W) | Lower (~0.5W for MachXO3) |

| Development Tools | Vivado (Complex) | Radiant/Diamond (Easier) |

| HDCP Support | Yes (Licensed IP) | Yes (ECP5) |

| Cost | $$$ | $ (MachXO3) / $$ (ECP5) |

For simple HDMI passthrough (1080p, dongles):

Use Lattice MachXO3 (cheap, low-power).

For 4K, video processing, or HDCP:

Use Xilinx Artix-7 or Lattice ECP5.

For learning/basic HDMI:

Start with Digilent HDMI PMOD (Spartan-6) or Lattice eval boards.