Time: 2025-05-30 11:11:52View:

FPGAs (Field-Programmable Gate Arrays) play a critical role in AESA radars due to their high-speed parallel processing, reconfigurability, and low-latency signal processing capabilities. Below is a breakdown of their functions and advantages in AESA systems.

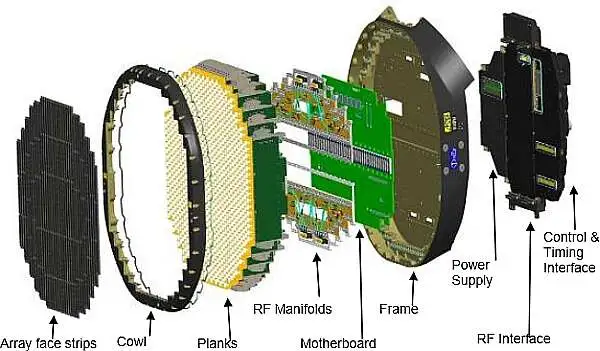

AESA radars use hundreds or thousands of transmit/receive (T/R) modules, each with its own phase shift for electronic beam steering.

FPGAs compute real-time phase shifts for each antenna element, enabling ultra-fast beam agility (microsecond-level steering).

They implement digital beamforming (DBF) algorithms, combining signals coherently for improved resolution and jamming resistance.

FPGAs handle real-time digital signal processing (DSP) tasks such as:

Fast Fourier Transform (FFT) for frequency-domain analysis.

Pulse compression (matched filtering) to improve range resolution.

Digital down-conversion (DDC) and up-conversion (DUC) for signal modulation.

Their parallel architecture allows multiple operations (e.g., filtering, demodulation) to run simultaneously, unlike sequential CPUs.

Modern AESAs use adaptive beamforming to suppress interference (e.g., jamming signals).

FPGAs implement adaptive algorithms like:

Space-Time Adaptive Processing (STAP) for moving target detection.

Minimum Variance Distortionless Response (MVDR) for interference rejection.

Radar systems require microsecond-level response times for tracking fast-moving threats.

FPGAs process raw ADC (Analog-to-Digital Converter) data directly, reducing latency compared to CPU/GPU-based systems.

Unlike ASICs (fixed hardware), FPGAs can be reprogrammed in the field to:

Adapt to new waveforms (e.g., switching between LFM, Barker codes).

Implement new threat countermeasures (e.g., anti-drone radar modes).

| Processor | Advantages | Disadvantages | Use Case in AESA |

|---|---|---|---|

| FPGA | Parallel processing, ultra-low latency, reconfigurable | Higher power consumption than ASICs, complex programming | Real-time beamforming, signal processing |

| ASIC | High efficiency, low power | Fixed function, expensive to redesign | Mass-produced military radars |

| CPU/GPU | Flexible, good for complex algorithms | High latency, sequential processing | Post-processing, AI-based target recognition |

Antenna Elements → Receive RF signals.

T/R Modules → Amplify and phase-shift signals.

ADCs → Convert analog signals to digital.

FPGA → Performs:

Beamforming (phase adjustments).

FFT & Pulse Compression (range/Doppler processing).

Clutter Rejection (STAP/MVDR).

CPU/GPU → Further analysis (e.g., target tracking, AI classification).

✔ Real-time processing (no OS delays).

✔ Reconfigurable for future threats.

✔ Radiation-hardened versions available for space/military use.

✔ Low-latency response (critical for missile defense).

SoC FPGAs (e.g., Xilinx Zynq, Intel Agilex) combine FPGA fabric with ARM CPUs for AI-enhanced radar processing.

Open FPGA standards (e.g., RISC-V integration) for more flexible military radar upgrades.

FPGAs are indispensable in AESA radars due to their high-speed, parallel, and reconfigurable nature, making them ideal for beamforming, signal processing, and electronic warfare applications.