Time: 2024-01-03 15:57:46View:

Clock signals are fundamental components in digital systems that synchronize the operation of various components within a computer or electronic device. These signals are used to coordinate the timing of operations, ensuring that different parts of the system work together harmoniously. In essence, a clock signal acts as a metronome for digital circuits, providing a regular rhythm that allows for the precise timing of data transmission, processing, and storage.

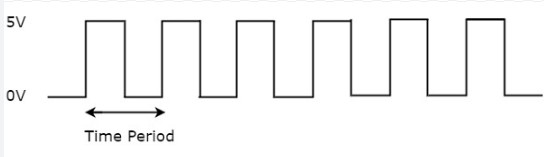

In digital electronics, the clock signal is typically a square wave that oscillates between two voltage levels at a constant frequency. This oscillation creates a series of high and low states, which are used to trigger specific actions within the system. For example, in a microprocessor, the rising edge or falling edge of the clock signal might indicate when a new instruction should be fetched or when data should be latched into a register.

The frequency of a clock signal is measured in hertz (Hz) and determines the speed at which a digital system operates. Higher clock frequencies allow for faster processing and data transfer, but they also require more power and can introduce additional challenges related to signal integrity and timing constraints.

Clock signals are crucial in ensuring the reliable and accurate operation of digital systems. Without proper synchronization, data corruption, timing errors, and other issues can arise, leading to malfunctions or system failures. As a result, the design and implementation of clock signals are carefully considered in the development of electronic devices and integrated circuits, with techniques such as clock distribution, skew management, and synchronization protocols playing key roles in achieving robust and efficient clocking schemes.

Clock signals are generated using various methods depending on the specific requirements of the digital system. One common approach involves the use of crystal oscillators, which are electronic circuits that utilize the mechanical resonance of a vibrating crystal to produce a precise and stable clock signal. These oscillators often consist of a quartz crystal that vibrates at a specific frequency when an electric field is applied, and the resulting oscillations are then converted into a square wave clock signal through additional circuitry.

Another method for generating clock signals is through the use of phase-locked loops (PLLs), which are versatile circuits capable of producing clock signals with adjustable frequencies and precise phase relationships. PLLs operate by comparing an input reference signal with a feedback signal derived from a voltage-controlled oscillator (VCO). By adjusting the VCO's frequency based on the phase and frequency differences between the input and feedback signals, PLLs can generate stable and accurate clock signals suitable for a wide range of applications.

In some cases, clock signals may also be generated using programmable clock generators or dedicated clock synthesis chips, which offer flexibility in producing multiple clock frequencies and output formats. These devices often feature configurable parameters such as frequency, duty cycle, and phase offset, allowing designers to tailor the clock signals to meet specific timing requirements and system constraints.

Furthermore, modern digital systems may employ advanced techniques such as spread-spectrum clocking, which intentionally modulates the frequency of the clock signal to reduce electromagnetic interference and improve signal integrity. This approach involves varying the clock frequency within a specified range, effectively spreading the energy of the signal across a wider frequency band and mitigating potential interference with other electronic components in the vemeko electronics.

Overall, the generation of clock signals is a critical aspect of digital system design, and the choice of a particular method depends on factors such as accuracy, stability, flexibility, and power consumption. By leveraging various techniques and technologies, engineers can create clock signals that meet the stringent timing requirements of today's complex electronic devices while ensuring reliable and efficient operation.

Clock signals come in various types, each serving specific purposes in digital systems. The most common types include the system clock, peripheral clock, and external clock.

The system clock, often referred to as the central processing unit (CPU) clock, is the primary timing reference for a digital system. It dictates the overall operational speed of the system and synchronizes the execution of instructions within the CPU and other core components. The system clock's frequency is typically determined by the requirements of the processor and influences the performance of the entire system, including the execution of instructions, data transfer rates, and overall responsiveness.

Peripheral clocks, on the other hand, are used to drive the operation of peripheral devices such as input/output (I/O) interfaces, timers, and communication modules. These clocks are often independent of the system clock and may operate at different frequencies to accommodate the diverse timing needs of peripheral components. By using separate peripheral clocks, digital systems can manage the timing of peripheral operations independently from the core processing activities, enhancing overall system efficiency and flexibility.

External clocks are signals sourced from external devices or components and are used to synchronize the operation of a digital system with external events or interfaces. For example, in embedded systems, external clocks may be derived from sensors, communication interfaces, or other interconnected devices to ensure proper coordination with external signals or data streams. These clocks enable seamless integration with external systems and facilitate the exchange of data and control signals across interconnected devices.

In addition to these primary types, there are specialized clock signals such as reference clocks, which provide precise timing references for high-speed data interfaces like Ethernet, USB, and PCIe. These clocks are critical for maintaining signal integrity and ensuring reliable data transmission in communication systems and high-speed interconnects.

Overall, the diverse types of clock signals cater to the specific timing requirements of different components and interfaces within digital systems, enabling efficient coordination and synchronization of operations across the entire system. By utilizing various clock types, designers can optimize the performance, reliability, and interoperability of digital devices in a wide range of applications.

In field-programmable gate arrays (FPGAs), clock signals play a crucial role in coordinating the operation of the configurable logic elements and other functional blocks within the device. FPGAs typically feature dedicated clock management resources that enable precise control and distribution of clock signals throughout the chip.

One key aspect of clock signals in FPGAs is the concept of global and regional clock networks. Global clock networks are designed to distribute clock signals across the entire FPGA chip, providing a common timing reference for synchronous operations. These networks are carefully engineered to minimize clock skew, ensuring that the arrival time of the clock signal at different parts of the chip is consistent, which is essential for maintaining synchronous behavior and reliable operation of the design.

In addition to global clock networks, FPGAs often incorporate regional clock resources that allow for the distribution of additional clock signals to specific areas or functional blocks within the device. These regional clocks enable the implementation of multi-clock designs, where different parts of the FPGA can operate at independent frequencies or be synchronized to different timing domains. This flexibility is valuable for accommodating diverse timing requirements and interfacing with external components operating at different clock speeds.

Clock signals in FPGAs are typically driven by dedicated clock input pins, which are connected to external sources such as crystal oscillators, clock buffers, or other clock generation circuits. Once inside the FPGA, these clock signals are routed through dedicated clock distribution networks, which are designed to minimize clock skew and ensure reliable and consistent timing across the chip.

FPGAs also offer advanced clock management features such as phase-locked loops (PLLs) and delay-locked loops (DLLs), which provide precise control over clock frequencies, phase relationships, and jitter reduction. These clock management resources enable designers to generate stable and low-jitter clock signals, synchronize multiple clock domains, and adapt to dynamic timing requirements in complex FPGA designs.

In short, clock signals in FPGAs are critical for achieving reliable and high-performance operation of digital designs. By leveraging sophisticated clock management resources and carefully engineered clock distribution networks, FPGAs empower designers to implement complex, multi-clock designs while ensuring robust synchronization and timing integrity across the entire chip.