Time: 2024-01-15 15:10:29View:

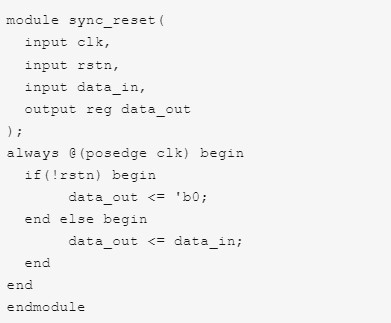

Synchronous reset is a technique used in digital circuit design to reset a flip-flop or a group of flip-flops in synchronization with the clock signal. In synchronous systems, the reset signal is typically synchronized to the clock to ensure that the reset operation occurs at a specific point in time, usually at the rising or falling edge of the clock signal. This synchronization helps to avoid timing hazards and ensures that the reset operation is performed predictably and reliably within the context of the system's clocked operation.

When a reset signal is applied synchronously to a flip-flop, it is typically asserted during a specific phase of the clock cycle, such as the rising or falling edge. This ensures that the reset operation occurs at a well-defined and predictable time, allowing the flip-flop to transition to its reset state in a controlled manner.

Synchronous reset is widely used in digital designs to ensure proper initialization of flip-flops and other sequential elements within a system.

Synchronous resets offer several advantages in digital circuit design. One of the key benefits is their ability to avoid timing hazards and metastability issues that can arise with asynchronous resets. By synchronizing the reset signal to the clock, designers can ensure that the reset operation occurs at a known and stable point in the system's timing, reducing the risk of unpredictable behavior. This predictability is crucial in ensuring the reliable operation of flip-flops and other sequential elements within a digital system.

Another advantage of synchronous resets is their compatibility with synchronous design methodologies. In synchronous systems, where all operations are coordinated and synchronized to a common clock signal, using synchronous resets aligns with the overall design philosophy. This can simplify the design process and make it easier to analyze and verify the behavior of the reset functionality within the context of the system's timing requirements.

However, synchronous resets also come with certain disadvantages. One potential drawback is the need for careful consideration of timing constraints and potential issues such as clock skew, setup and hold times, and the overall timing relationship between the reset signal and the clock. Designers must ensure that the reset signal is synchronized effectively with the clock signal to avoid introducing timing issues that could impact the reliability of the reset operation.

Additionally, synchronous resets may introduce additional complexity in the design, particularly when dealing with multi-clock domain systems or when integrating reset functionality across different parts of a larger digital system. Managing the synchronization of reset signals across different clock domains and ensuring proper reset release timing can require careful attention to detail and may add complexity to the overall design process.

In summary, while synchronous resets offer advantages such as predictable timing behavior and compatibility with synchronous design methodologies, they also require careful consideration of timing constraints and potential complexity in multi-clock domain systems. Designers must weigh these factors when deciding whether to use synchronous resets in their digital designs and implement appropriate design practices to ensure reliable and predictable operation of the reset functionality.

Asynchronous reset is a technique used in digital circuit design to reset a flip-flop or a group of flip-flops without being synchronized to the clock signal. In synchronous systems, the reset signal is typically synchronized to the clock to ensure that the reset operation occurs at a specific point in time, usually at the rising or falling edge of the clock signal. However, in asynchronous reset, the reset signal can be asserted at any time, independent of the clock signal.

When a reset signal is applied asynchronously to a flip-flop, it forces the flip-flop into a known state, typically the reset state, regardless of the current clock cycle. This can be useful in situations where a system needs to be reset immediately, without waiting for the next clock cycle. However, asynchronous reset can introduce timing hazards and metastability issues if not implemented carefully.

Designers should carefully consider the trade-offs and potential hazards associated with asynchronous reset and implement appropriate techniques to ensure reliable operation within their specific design context.

Asynchronous resets offer certain advantages in digital circuit design. One of the key benefits is their ability to provide immediate and independent reset functionality, as the reset signal can be asserted at any time, independent of the clock signal. This can be particularly useful in situations where a system needs to be reset immediately, without waiting for the next clock cycle. Asynchronous resets can thus offer a more responsive and flexible reset capability compared to synchronous resets.

Another advantage of asynchronous resets is their potential to simplify the design process in certain scenarios. In designs where immediate reset functionality is a priority, using asynchronous resets can eliminate the need to carefully manage the timing relationship between the reset signal and the clock, potentially reducing design complexity and easing timing constraints in certain parts of the system.

However, asynchronous resets also come with certain disadvantages. One potential drawback is the risk of timing hazards and metastability issues if not implemented carefully. When a reset signal arrives at a flip-flop while it is in the process of changing state due to a clock edge, it can lead to metastability, causing the flip-flop to enter an unpredictable state for a brief period of time. Mitigating this risk may require additional circuitry such as synchronizers and pulse-stretching circuits, adding complexity to the design.

Another potential disadvantage of asynchronous resets is their compatibility with synchronous design methodologies. In systems where all operations are coordinated and synchronized to a common clock signal, integrating asynchronous resets may introduce additional complexity and require careful consideration of timing relationships and potential hazards, particularly in multi-clock domain systems.

In summary, while asynchronous resets offer advantages such as immediate and independent reset functionality, they also come with potential risks such as timing hazards and metastability issues if not implemented carefully. Designers must carefully weigh these factors when deciding whether to use asynchronous resets in their digital designs and implement appropriate design practices to ensure reliable and predictable operation of the reset functionality.

Aspect | Asynchronous Resets | Synchronous Resets |

Timing Dependencies | Independent of the clock signal, immediate reset capability | Synchronized to the clock signal, reset occurs at a specific clock phase |

Metastability Risk | Higher risk without proper implementation | Lower risk due to synchronization with the clock signal |

Design Complexity | Potential for simpler design in certain scenarios | May introduce additional complexity, especially in multi-clock domain systems |

Compatibility | May not align with synchronous design methodologies | Aligns with synchronous design methodologies in clocked systems |

Responsiveness | Immediate and independent reset capability | Reset occurs at a specific clock phase, may not be immediate |

Implementation Overhead | May require additional circuitry for hazard mitigation | Requires careful consideration of timing constraints and potential hazards |

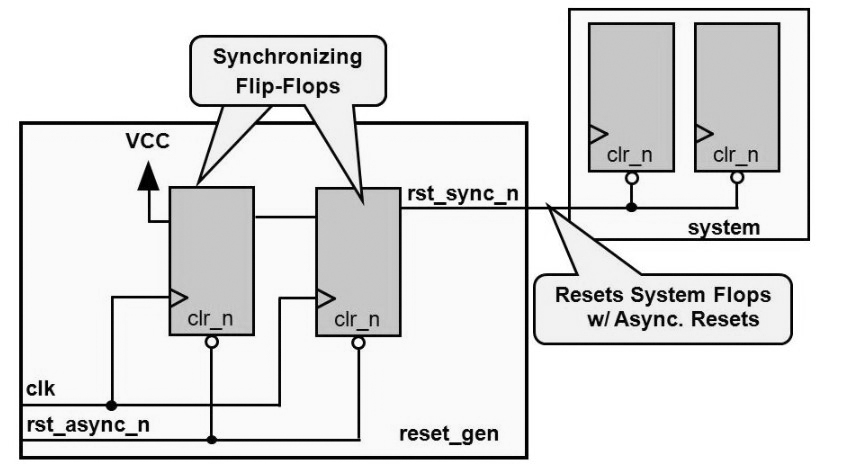

Asynchronous reset with synchronous release is a technique used in digital circuit design to reset a flip-flop or a group of flip-flops asynchronously, but release the reset synchronously. This approach combines the immediate and independent reset capability of asynchronous resets with the controlled and predictable release timing of synchronous resets.

When a reset signal is applied asynchronously to a flip-flop, it forces the flip-flop into a known state, typically the reset state, regardless of the current clock cycle. This immediate reset capability can be valuable in situations where a system needs to be reset without waiting for the next clock cycle. However, to ensure reliable and predictable operation, the release of the reset signal is synchronized to the clock, allowing the flip-flop to transition to its active state at a specific point in the clock cycle.

The use of asynchronous reset with synchronous release helps to mitigate the potential hazards and metastability issues associated with asynchronous resets. By synchronizing the release of the reset signal to the clock, designers can ensure that the flip-flop transitions to its active state at a well-defined and predictable time, reducing the risk of unpredictable behavior and potential timing issues.

This approach can be particularly useful in designs where immediate reset functionality is required, but the release of the reset signal needs to be coordinated with the system's clocked operation. It allows designers to take advantage of the responsiveness of asynchronous resets while ensuring that the reset release occurs in a controlled and predictable manner, aligning with the overall synchronous design methodologies.

Implementing asynchronous reset with synchronous release requires careful consideration of timing constraints and potential hazards, as well as the use of appropriate circuitry to ensure proper synchronization and release timing. Designers must weigh the trade-offs and potential complexities associated with this approach, but when implemented effectively, it can offer a valuable combination of immediate reset capability and controlled release timing within digital designs.

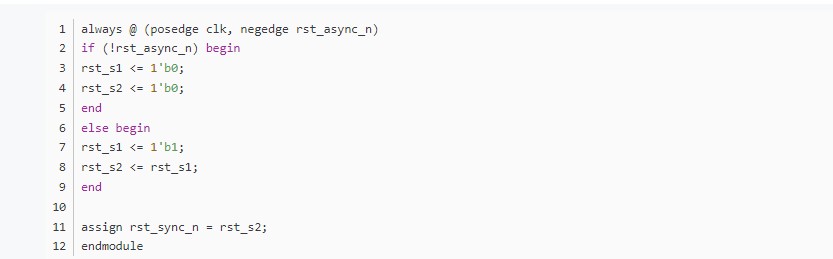

The code to achieved this as below:

In practical applications, the choice of the appropriate reset method depends on specific design requirements and operating environments. However, in actual Verilog code writing, we commonly use the asynchronous reset method.