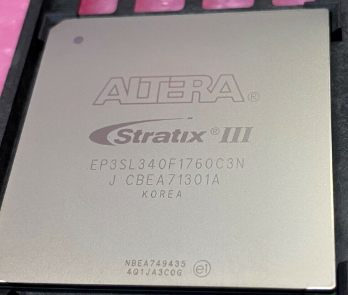

One of the most technologically sophisticated, high-performance, low-power FPGAs on the market is offered by the Stratix® III family. Through Altera's ground-breaking Programmable Power Technology, which enables the ability to turn on performance when needed and reduce power consumption for blocks that are not in use, Stratix III FPGAs utilize less power. To produce the industry's lowest power, high-performance FPGAs, the latest silicon process optimizations and selectable core voltage are also used.

High-speed I/O is made efficient and flexible by modular I/O banks with a common bank structure enabling vertical migration. Best-in-class signal integrity is provided by package and die upgrades with dynamic on-chip termination, output delay, and current intensity control. The Stratix III family is a programmable alternative to proprietary ASICs and programmable processors for high-performance logic, digital signal processing (DSP), and embedded designs. It is based on a 1.1-V, 65-nm all-layer copper SRAM process.

Stratix III devices offer 256-bit Advanced Encryption Standard (AES) encryption as an optional configuration bit stream security measure. The configuration random-access memory (CRAM) and user memory cells in Stratix III devices have automatic error detection circuitry built in to identify data corruption caused by soft faults when ultra-high reliability is required.