Time: 2025-01-08 10:40:58View:

1. Introduction

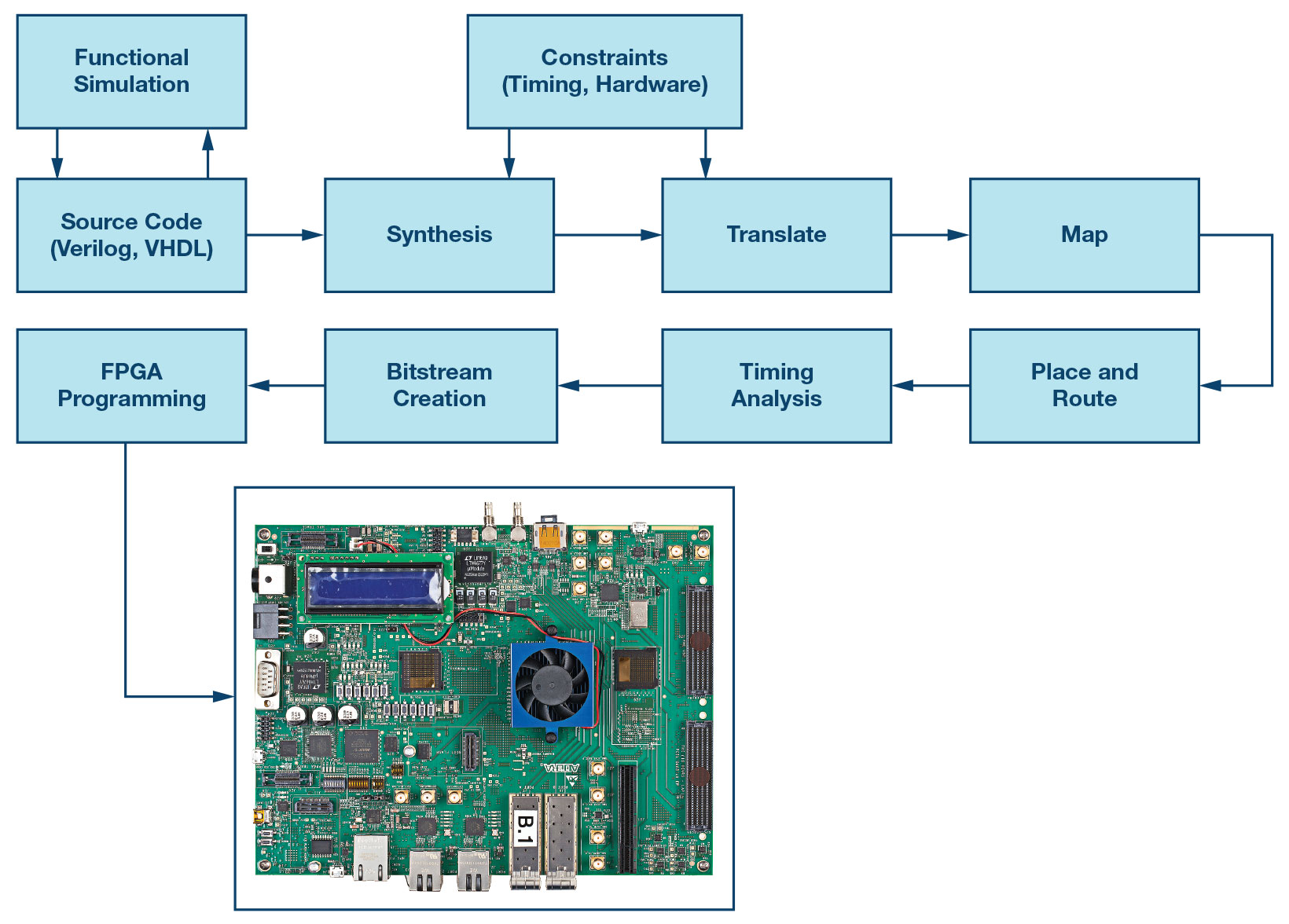

With the rapid development of semiconductor and chip technology, FPGA now integrates more and more configurable logic resources, various external bus interfaces, and rich internal RAM resources, making it increasingly widely used in fields such as national defense, healthcare, and consumer electronics. When designing circuits using FPGA, most FPGAs have requirements for power on sequencing and timing, so power sequencing is an important aspect to consider. Usually, FPGA suppliers have specified requirements for power sorting and power on time. Because the number of power rails required for an FPGA varies from 3 to 10 or more. By following the recommended power sequence, it is possible to avoid drawing excessive current during startup while also preventing device damage. There are multiple methods for sorting the power supplies in the smallest circuit of an FPGA. This article mainly takes MP5650 as an example to describe cascading PGOOD pins to enable pins to achieve sorting.

2. Research and Development Cases

The case shared today is based on the K7 core board developed, named MP5650. The MP5650 adopts the XC7K325T-2FG900I/XC7K410T-2FFG900I from the XILINX Kintex-7 series as the main controller. Four DDR3 storage chips are mounted on the HP port of the FPGA chip, with each DDR3 chip having a capacity of up to 512MB bytes and a data bit width of 64 bits composed of 16 bits per chip. One 128Mb QSPI FLASH chip is used for static storage of FPGA chip configuration files or other user data. The core board is connected to the base board using four gold-plated connectors with a spacing of 0.5mm and 120 pins. Four 3.5mm fixing holes are placed on the four pins of the core board, which can be fastened to the base board with screws to ensure stable operation in strong vibration environments. The dimensions of the core board structure are 65 (mm) × 85 (mm). This board is very suitable for high-speed data communication; Video capture, video output, consumer electronics; Machine vision, industrial control; Pre validation of project development; Electronic information engineering, automation, communication engineering, and other related fields and populations for developers to study.

The power rails required for K7FPGA of MP5650 are as follows:

(1)VCCINT

FPGA internal core voltage. The range that does not damage FPGA devices is -0.5V~1.1V, and the normal operating voltage is 0.97V~1.03V. The recommended operating voltage is 1.0V.

(2)VCCAUX

Auxiliary power supply voltage. The range that does not damage FPGA devices is -0.5V~2.0V. The normal operating voltage is 1.71V~1.89V. The recommended working voltage is 1.8V.

(3)VCCBRAM

Power supply voltage for internal Block RAM. The range that does not damage FPGA devices is -0.5V~1.1V. The normal operating voltage is 0.97V~1.03V, and the recommended operating voltage is 1.00V.

(4)VCCIO

For the interface voltage of HR BANK, it needs to be consistent with the signal level of external devices, and the range that does not damage FPGA devices is -0.5V~3.6V. The normal operating voltage is 1.14V~3.465V. The recommended working voltage should be consistent with the external signal level. For the interface voltage of HP BANK, it needs to be consistent with the signal level of external devices, and the range that does not damage FPGA devices is -0.5V~2.0V. The normal operating voltage is 1.14V~1.89V. The recommended working voltage should be consistent with the external signal level.

(5)VCCAUX_IO

IO auxiliary voltage. The range that does not damage FPGA devices is -0.5V~2.06V. The normal operating voltage is 1.14V~1.89V/2.06V. The recommended working voltage is 1.8V/2V.

(6)VCCADC

The supply voltage of XADC. The range that does not damage FPGA devices is -0.5V~2.0V. The normal operating voltage is 1.71V~1.89V. The recommended working voltage is 1.80V.

(7)MGTAVCC

GTX transceiver core voltage. The range that does not damage FPGA devices is -0.5V~1.1V. The normal operating voltage is 0.97V~1.08V, and the recommended operating voltage is 1.00V.

(8)MGTAVTT

GTX transceiver terminal matching voltage. Its range of not damaging FPGA devices is -0.5V~1.32V. The normal operating voltage is 1.17V~1.23V. The recommended working voltage is 1.20V.

(9)MGTVCCAUX

GTX transceiver auxiliary voltage. The range that does not damage FPGA devices is -0.5V~1.935V. The normal operating voltage is 1.75V~1.85V. The recommended working voltage is 1.80V.

(10)MGTAVTTRCAL

GTX transceiver calibration voltage. Its range of not damaging FPGA devices is -0.5V~1.32V. The normal operating voltage is 1.17V~1.23V. The recommended working voltage is 1.20V.

The official recommended power on sequence is VCCINT VCCBRAM、VCCAUX、VCCAUX_IO、VCCO, The power-off sequence is exactly opposite to the power on sequence. In addition, if the VCCINT and VCCBRAM power rails are consistent, they can be powered on/off simultaneously. VCCAUX_IO, VCCAUX, and VCCO power rails can also be powered on/off simultaneously. Other power rails have no power sequence. The power on sequence of GTX transceiver is VCCINT, MGTAVCC, MGTAVTT or MGTAVCC VCCINT、MGTAVTT。 The power-off sequence is exactly the opposite. MGTVCCAUX has no order.

3. MP5650 power sorting method

One method of implementing sorting is to cascade the Power Good (PGOOD) pin of one power supply to the Enable (EN) pin of the subsequent power supply. The power chip starts to turn on when the PG threshold is met. The advantage of this method is low cost, but it cannot easily control timing. Add a capacitor to the EN pin to introduce a timing delay in the power on cascade.

The DC-DC power chips used on MP5650 are LTM4628 and LTNM4622. The chip changes the power on time by controlling the TRACK/SS pin and applying a capacitor to the pin. The smaller the capacitance, the shorter the power on time. If there are multiple levels of FPGA power supply, and the power on time for each level is too long, it will cause the total power on time of the power supply to be too slow, exceeding the maximum value given by the official, resulting in the inability to start configuration work and abnormal FPGA operation. The official power on time requirement is with a maximum of 50ms.

In our initial design, the TRACK/SS pin capacitance was selected as 0.1uF. We found that after four levels of cascading, sometimes the Flash configuration chip configuration was not successful when powered on. After oscilloscope testing, it was found that the power on time was too long, exceeding Xilinx's requirement of 50ms. After modifying the TRACK/SS pin capacitance to 4.7nF, the power on time is greatly reduced, which is about 3ms. Satisfied Xilinx's power on time requirements, FPGA can work normally. In the design, the TRACK/SS pin can also be suspended, and by default, the power on time has a default delay time of about a few hundred microseconds.

4. Summary

Overall, the power structure of kintex7 FPGA is quite complex. At present, the power supply scheme for the 7 series FPGA with power on sequence designed by users is commonly controlled by the input EN and output PGOOD of each power chip to control the sequence, and the power on time needs to meet Xilinx's official requirements. By starting the description, we can clearly see the interfaces and functions contained in this MP5650 core board. For users who require a large amount of IO, this core board would be a good choice. Moreover, in the IO connection section, the wiring between the same BANK pin and the connector interface has undergone equal length and differential processing, which is very suitable for secondary development.