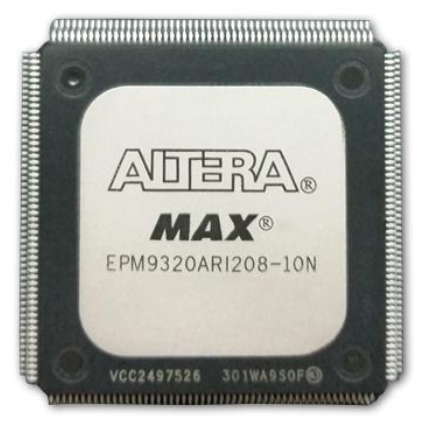

The third-generation MAX architecture from Altera serves as the foundation for the MAX 9000 family of in-system programmable, high-density, high-performance EPLDs. The EEPROM-based MAX 9000 family, which is constructed using cutting-edge CMOS technology, has 6,000–12,000 useable gates, pin-to-pin delays as quick as 10 ns, and counter rates as high as 144 MHz.

Four distinct inputs with huge fan-outs are provided in all MAX 9000 device packages for global control signals. Each I/O pin has a corresponding I/O cell register and a clock enable control on the device's edge. These registers offer short clock-to-output and setup times when used as inputs and outputs, respectively.

In-system programmability (ISP) of 5.0-V is offered by MAX 9000 EPLDs. For quick and effective iterations during design development and debug cycles, this capability enables the devices to be programmed and reprogrammed on the printed circuit board (PCB). The MAX 9000 devices come with a 100 program/erase cycle warranty.