Time: 2025-05-15 11:22:54View:

Field-Programmable Gate Arrays (FPGAs) are reconfigurable integrated circuits used for implementing digital logic, signal processing, and embedded systems. Unlike microcontrollers, FPGAs allow parallel processing and hardware-level customization, making them ideal for high-speed, low-latency applications.

An FPGA consists of:

Configurable Logic Blocks (CLBs) – Basic logic units (LUTs, flip-flops).

Programmable Interconnects – Routes signals between blocks.

I/O Blocks – Interface with external components.

DSP Slices & Block RAM – For math operations and data storage.

| Feature | FPGA | Microcontroller |

|---|---|---|

| Processing | Parallel (Hardware) | Sequential (Software) |

| Flexibility | Reconfigurable logic | Fixed architecture |

| Speed | High (Nanosecond latency) | Lower (Millisecond latency) |

| Use Cases | DSP, ASIC prototyping, robotics | Embedded control, IoT |

Hardware Description Languages (HDLs):

VHDL (Strongly typed, common in Europe).

Verilog (C-like syntax, popular in the US).

Example (Verilog):

module blink_led ( input clk, output reg led); reg [31:0] counter; always @(posedge clk) begin counter <= counter + 1; if (counter >= 50_000_000) begin led <= ~led; counter <= 0; end endendmodule

Use ModelSim, Vivado Simulator, or iverilog to verify logic.

Example testbench:

`timescale 1ns/1psmodule tb_blink(); reg clk; wire led; blink_led uut (clk, led); initial begin clk = 0; forever #5 clk = ~clk; // 100 MHz clock end initial #1000 $finish;endmodule

Tools: Xilinx Vivado, Intel Quartus, or Lattice Diamond.

Converts HDL into a netlist and maps it to FPGA resources.

Generate a .bit or .sof file and flash it to the FPGA via JTAG/USB.

Combinational: Output depends only on current inputs (e.g., AND gates).

Sequential: Output depends on current inputs + past states (e.g., flip-flops).

Used for control logic. Example (Traffic Light Controller):

module traffic_light ( input clk, reset, output reg red, yellow, green); reg [1:0] state; parameter S_RED = 0, S_GREEN = 1, S_YELLOW = 2; always @(posedge clk or posedge reset) begin if (reset) state <= S_RED; else case (state) S_RED: begin red=1; green=0; yellow=0; state <= S_GREEN; end S_GREEN: begin red=0; green=1; yellow=0; state <= S_YELLOW; end S_YELLOW: begin red=0; green=0; yellow=1; state <= S_RED; end endcase endendmodule

Breaks operations into stages to improve clock speed.

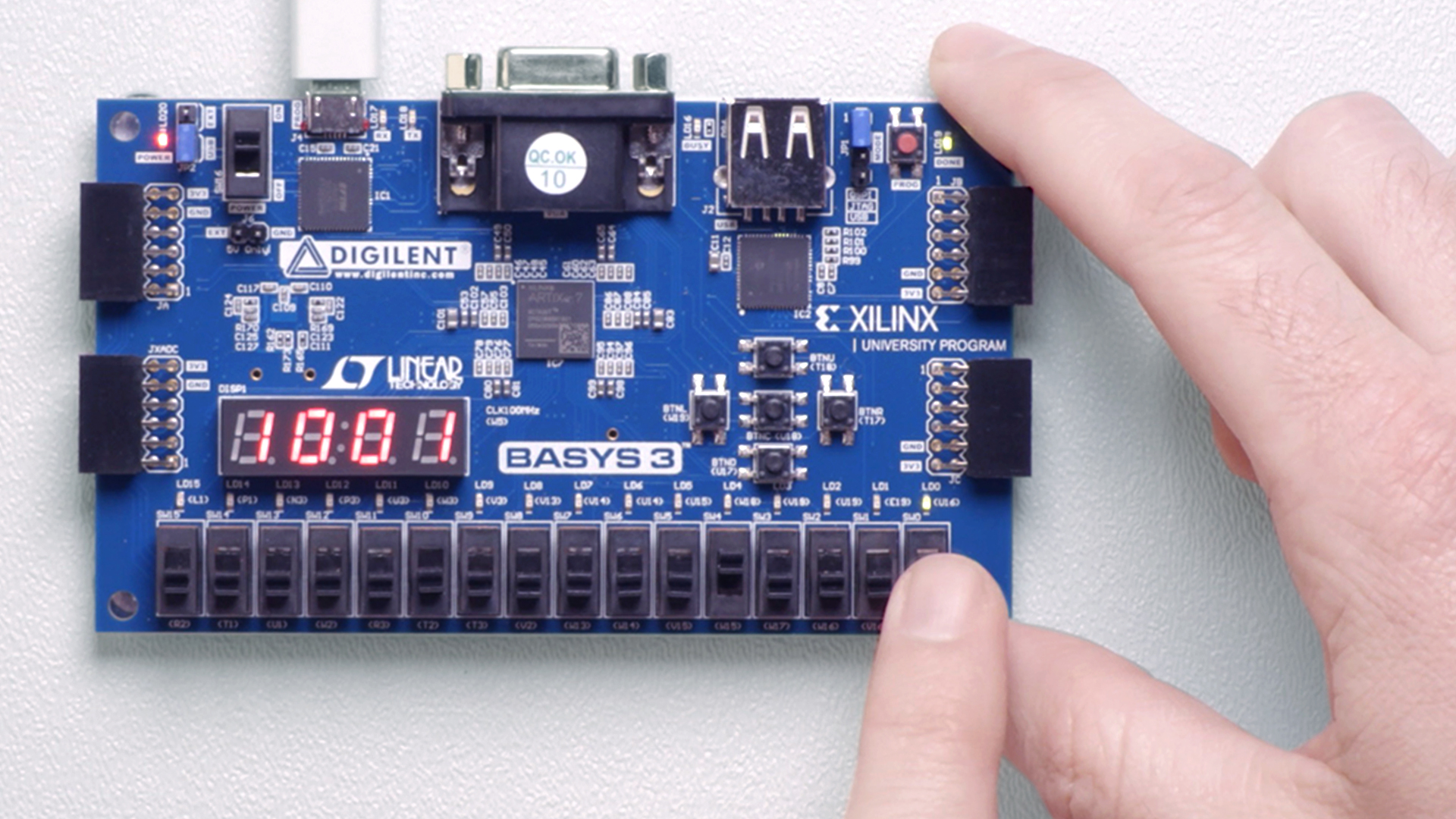

| Board | FPGA Chip | Vendor | Price Range |

|---|---|---|---|

| Xilinx Pynq-Z1 | Zynq-7000 | Xilinx | 300 |

| DE10-Nano | Cyclone V | Intel | 200 |

| Basys 3 | Artix-7 | Xilinx | 200 |

| TinyFPGA | iCE40 | Lattice | 100 |

module pwm_led ( input clk, input [7:0] duty_cycle, output reg led); reg [7:0] counter; always @(posedge clk) begin counter <= counter + 1; led <= (counter < duty_cycle) ? 1 : 0; endendmodule

Write the HDL code.

Simulate with a testbench.

Synthesize and program the FPGA.

Connect an LED to an FPGA GPIO pin.

High-Level Synthesis (HLS) – Write C/C++ code (Xilinx Vitis HLS).

Soft-Core Processors (e.g., MicroBlaze, Nios II).

FPGA Accelerators (AI/ML, cryptography).

Books:

FPGA Prototyping by Verilog Examples (Pong Chu).

Free Range VHDL (Bryan Mealy).

Online Courses:

Coursera: FPGA Design for Embedded Systems (University of Colorado).

Udemy: Learn VHDL and FPGA Development.

Tools:

Xilinx Vivado (Free WebPack Edition).

Intel Quartus Prime Lite.

FPGAs offer unparalleled flexibility for digital design. Start with simple projects (LED blink, PWM) and progress to complex systems (DSP, robotics).